Planar process

The planar process is a manufacturing process used in the semiconductor industry to build individual components of a transistor, and in turn, connect those transistors together. It is the primary process by which silicon integrated circuit chips are built. The process utilizes the surface passivation and thermal oxidation methods.

The planar process was developed at Fairchild Semiconductor in 1959 by Jean Hoerni, who adopted the surface passivation and thermal oxidation methods originally developed by Mohamed Atalla at Bell Labs in 1957. Hoerni's planar process was in turn the basis for Robert Noyce's invention of the monolithic integrated circuit chip at Fairchild, later in 1959.

Overview

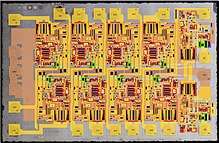

The key concept is to view a circuit in its two-dimensional projection (a plane), thus allowing the use of photographic processing concepts such as film negatives to mask the projection of light exposed chemicals. This allows the use of a series of exposures on a substrate (silicon) to create silicon oxide (insulators) or doped regions (conductors). Together with the use of metallization, and the concepts of p–n junction isolation and surface passivation, it is possible to create circuits on a single silicon crystal slice (a wafer) from a monocrystalline silicon boule.

The process involves the basic procedures of silicon dioxide (SiO2) oxidation, SiO2 etching and heat diffusion. The final steps involves oxidizing the entire wafer with an SiO2 layer, etching contact vias to the transistors, and depositing a covering metal layer over the oxide, thus connecting the transistors without manually wiring them together.

History

Background

In 1955, Carl Frosch and Lincoln Derick at Bell Telephone Laboratories (BTL) accidentally discovered that silicon dioxide could be grown on silicon.[1] Later in 1958, they proposed that silicon oxide layers could protect silicon surfaces during diffusion processes, and could be used for diffusion masking.[2][3]

Surface passivation, the process by which a semiconductor surface is rendered inert, and does not change semiconductor properties as a result of interaction with air or other materials in contact with the surface or edge of the crystal,[4] was first developed by Egyptian engineer Mohamed M. Atalla at BTL in the late 1950s.[5][6] He discovered that the formation of a thermally grown silicon dioxide (SiO2) layer greatly reduced the concentration of electronic states at the silicon surface,[6] and discovered the important quality of SiO2 films to preserve the electrical characteristics of p–n junctions and prevent these electrical characteristics from deteriorating by the gaseous ambient environment.[3] He found that silicon oxide layers could be used to electrically stabilize silicon surfaces.[2] He developed the surface passivation process, a new method of semiconductor device fabrication that involves coating a silicon wafer with an insulating layer of silicon oxide so that electricity could reliably penetrate to the conducting silicon below. By growing a layer of silicon dioxide on top of a silicon wafer, Atalla was able to overcome the surface states that prevented electricity from reaching the semiconducting layer.[5][7]

Atalla first published his findings in 1957.[8][9] According to Fairchild Semiconductor engineer Chih-Tang Sah, the surface passivation process developed by Atalla and his team was "the most important and significant technology advance, which blazed the trail" that led to the silicon integrated circuit.[10][11][12]

Development

At a 1958 Electrochemical Society meeting, Mohamed Atalla presented a paper about the surface passivation of PN junctions by thermal oxidation, based on his 1957 BTL memos,[13] and demonstrated silicon dioxide's passivating effect on a silicon surface.[9] This was the first demonstration to show that high-quality silicon dioxide insulator films could be grown thermally on the silicon surface to protect the underlying silicon p-n junction diodes and transistors.[3]

Swiss engineer Jean Hoerni attended the same 1958 meeting, and was intrigued by Atalla's presentation. Hoerni came up with the "planar idea" one morning while thinking about Atalla's device.[13] Taking advantage of silicon dioxide's passivating effect on the silicon surface, Hoerni proposed to make transistors that were protected by a layer of silicon dioxide.[13] This led to the first successful product implementation of the Atalla silicon transistor passivation technique by thermal oxide.[14]

The planar process was developed by Jean Hoerni, one of the "traitorous eight", while working at Fairchild Semiconductor, with a first patent issued 1959.[15][16]

Together with the use of metallization (to join together the integrated circuits), and the concept of p–n junction isolation (from Kurt Lehovec), the researchers at Fairchild were able to create circuits on a single silicon crystal slice (a wafer) from a monocrystalline silicon boule.

In 1959, Robert Noyce built on Hoerni's work with his conception of an integrated circuit (IC), which added a layer of metal to the top of Hoerni's basic structure to connect different components, such as transistors, capacitors, or resistors, located on the same piece of silicon. The planar process provided a powerful way of implementing an integrated circuit that was superior to earlier conceptions of the integrated circuit.[9] Noyce's invention was the first monolithic IC chip.[17][18]

Early versions of the planar process used a photolithography process using near-ultraviolet light from a mercury vapor lamp. As of 2011, small features are typically made with 193 nm "deep" UV lithography.[19] Some researchers use even higher-energy extreme ultraviolet lithography.

See also

References

- Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. pp. 22–23. ISBN 9780801886393.

- Lécuyer, Christophe; Brock, David C. (2010). Makers of the Microchip: A Documentary History of Fairchild Semiconductor. MIT Press. p. 111. ISBN 9780262294324.

- Saxena, A (2009). Invention of integrated circuits: untold important facts. International series on advances in solid state electronics and technology. World Scientific. pp. 96–97. ISBN 9789812814456.

- "Surface Passivation - an overview". ScienceDirect. Retrieved 19 August 2019.

- "Martin Atalla in Inventors Hall of Fame, 2009". Retrieved 21 June 2013.

- Black, Lachlan E. (2016). New Perspectives on Surface Passivation: Understanding the Si-Al2O3 Interface. Springer. p. 17. ISBN 9783319325217.

- "Dawon Kahng". National Inventors Hall of Fame. Retrieved 27 June 2019.

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. pp. 120 & 321–323. ISBN 9783540342588.

- Bassett, Ross Knox (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. Johns Hopkins University Press. p. 46. ISBN 9780801886393.

- Wolf, Stanley (March 1992). "A review of IC isolation technologies". Solid State Technology: 63.

- Huff, Howard R.; Tsuya, H.; Gösele, U. (1998). Silicon Materials Science and Technology: Proceedings of the Eighth International Symposium on Silicon Materials Science and Technology. Electrochemical Society. pp. 181–182.

- Sah, Chih-Tang (October 1988). "Evolution of the MOS transistor-from conception to VLSI" (PDF). Proceedings of the IEEE. 76 (10): 1280–1326 (1290). Bibcode:1988IEEEP..76.1280S. doi:10.1109/5.16328. ISSN 0018-9219.

- Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. p. 120. ISBN 9783540342588.

- Sah, Chih-Tang (October 1988). "Evolution of the MOS transistor-from conception to VLSI" (PDF). Proceedings of the IEEE. 76 (10): 1280–1326 (1291). Bibcode:1988IEEEP..76.1280S. doi:10.1109/5.16328. ISSN 0018-9219.

- US 3025589 Hoerni, J. A.: "Method of Manufacturing Semiconductor Devices” filed May 1, 1959

- US 3064167 Hoerni, J. A.: "Semiconductor device" filed May 15, 1960

- "1959: Practical Monolithic Integrated Circuit Concept Patented". Computer History Museum. Retrieved 13 August 2019.

- "Integrated circuits". NASA. Retrieved 13 August 2019.

- Shannon Hill. "UV Lithography: Taking Extreme Measures". National Institute of Standards and Technology (NIST).

External links

- "The silicon engine: A timeline of semiconductors in computing". Timeline: Browse by decade. Computer history museum. 2012. Retrieved 2012-06-03. A compendium of articles and other information on the development of integrated circuits, including the development of oxide masking, photolithography, the advent of silicon, the integrated circuit and the planar process.

- The Planar Process

- "The history of the integrated circuit". Nobelprize.org. 2003. Retrieved 2012-06-03. An overview of the steps in fabrication of an integrated circuit from the Nobel Prize website. This is a section of the work Techville: The integrated circuit.