Address decoder

In digital electronics, an address decoder is a binary decoder that has two or more inputs for address bits and one or more outputs for device selection signals.[1] When the address for a particular device appears on the address inputs, the decoder asserts the selection output for that device. A dedicated, single-output address decoder may be incorporated into each device on an address bus, or a single address decoder may serve multiple devices.[2]

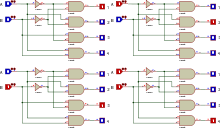

A single address decoder with n address input bits can serve up to 2n devices. Several members of the 7400 series of integrated circuits can be used as address decoders. For example, when used as an address decoder, the 74154[3] provides four address inputs and sixteen (i.e., 24) device selector outputs. An address decoder is a particular use of a binary decoder circuit known as a "demultiplexer" or "demux" (the 74154 is commonly called a "4-to-16 demultiplexer"), which has many other uses besides address decoding.

Address decoders are fundamental building blocks for systems that use buses. They are represented in all integrated circuit families and processes and in all standard FPGA and ASIC libraries. They are discussed in introductory textbooks in digital logic design.[1]

References

- 1 2 Paul Horowitz and Winfield Hill (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 685,766. ISBN 978-0-521-37095-0.

- ↑ S. J. Cahill (1993). Digital and microprocessor engineering (2nd ed.). Ellis Horwood. pp. 489–494. ISBN 978-0-13-213398-2.

- ↑ Datasheet for 74HC154

External links