Wallace tree

A Wallace tree is an efficient hardware implementation of a digital circuit that multiplies two integers, devised by Australian Computer Scientist Chris Wallace in 1964.[1]

The Wallace tree has three steps:

- Multiply (that is – AND) each bit of one of the arguments, by each bit of the other, yielding results. Depending on position of the multiplied bits, the wires carry different weights, for example wire of bit carrying result of is 128 (see explanation of weights below).

- Reduce the number of partial products to two by layers of full and half adders.

- Group the wires in two numbers, and add them with a conventional adder.[2]

The second step works as follows. As long as there are three or more wires with the same weight add a following layer:

- Take any three wires with the same weights and input them into a full adder. The result will be an output wire of the same weight and an output wire with a higher weight for each three input wires.

- If there are two wires of the same weight left, input them into a half adder.

- If there is just one wire left, connect it to the next layer.

The benefit of the Wallace tree is that there are only reduction layers, and each layer has propagation delay. As making the partial products is and the final addition is , the multiplication is only , not much slower than addition (however, much more expensive in the gate count). Naively adding partial products with regular adders would require time. From a complexity theoretic perspective, the Wallace tree algorithm puts multiplication in the class NC1.

These computations only consider gate delays and don't deal with wire delays, which can also be very substantial.

The Wallace tree can be also represented by a tree of 3/2 or 4/2 adders.

It is sometimes combined with Booth encoding.[3][4]

Weights explained

The weight of a wire is the radix (to base 2) of the digit that the wire carries. In general, – have indexes of and ; and since the weight of is .

Example

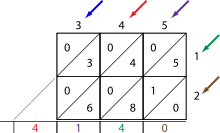

, multiplying by :

- First we multiply every bit by every bit:

- weight 1 –

- weight 2 – ,

- weight 4 – , ,

- weight 8 – , , ,

- weight 16 – , ,

- weight 32 – ,

- weight 64 –

- Reduction layer 1:

- Pass the only weight-1 wire through, output: 1 weight-1 wire

- Add a half adder for weight 2, outputs: 1 weight-2 wire, 1 weight-4 wire

- Add a full adder for weight 4, outputs: 1 weight-4 wire, 1 weight-8 wire

- Add a full adder for weight 8, and pass the remaining wire through, outputs: 2 weight-8 wires, 1 weight-16 wire

- Add a full adder for weight 16, outputs: 1 weight-16 wire, 1 weight-32 wire

- Add a half adder for weight 32, outputs: 1 weight-32 wire, 1 weight-64 wire

- Pass the only weight-64 wire through, output: 1 weight-64 wire

- Wires at the output of reduction layer 1:

- weight 1 – 1

- weight 2 – 1

- weight 4 – 2

- weight 8 – 3

- weight 16 – 2

- weight 32 – 2

- weight 64 – 2

- Reduction layer 2:

- Add a full adder for weight 8, and half adders for weights 4, 16, 32, 64

- Outputs:

- weight 1 – 1

- weight 2 – 1

- weight 4 – 1

- weight 8 – 2

- weight 16 – 2

- weight 32 – 2

- weight 64 – 2

- weight 128 – 1

- Group the wires into a pair of integers and an adder to add them.

See also

References

- ↑ Wallace, Christopher Stewart (February 1964). "A suggestion for a fast multiplier". IEEE Transactions on Electronic Computers. EC-13 (1): 14–17.

- ↑ Bohsali, Mounir; Doan, Michael (2010). "Rectangular Styled Wallace Tree Multipliers" (PDF). Archived from the original (PDF) on 2010-02-15.

- ↑ "Introduction". 8x8 Booth Encoded Wallace-tree multiplier. Tufts university. 2007. Archived from the original on 2010-06-17.

- ↑ Weems Jr., Charles C. (2001) [1995]. "CmpSci 535 Discussion 7: Number Representations". Amherst: University of Massachusetts. Archived from the original on 2011-02-06.

Further reading

- Savard, John J. G. (2018) [2006]. "Advanced Arithmetic Techniques". quadibloc. Archived from the original on 2018-07-03. Retrieved 2018-07-16.