Single-electron transistor

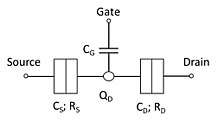

A single-electron transistor (SET) is a sensitive electronic device based on the Coulomb blockade effect. In this device the electron flows through a tunnel junction between source/drain to a quantum dot (conductive island). Moreover, the electrical potential of the island can be tuned by a third electrode, known as the gate, which is capacitively coupled to the island. Fig. 1 shows the basic schematic of a SET device. The conductive island is sandwiched between two tunnel junctions,[1] which are modeled by a capacitance (CD and CS) and a resistor (RD and RS) in parallel.

Introduction

The increasing relevance of the Internet of things and the healthcare applications give more relevant impact to the electronic device power consumption. For this purpose, ultra-low-power consumption is one of the main research topics into the current electronics world. The amazing number of tiny computers used in the day-to-day world, e.g. mobile phones and home electronics; requires a significant power consumption level of the implemented devices. In this scenario, the single-electron transistor has appeared as a suitable candidate to achieve this low power range with high level of device integration. The main technological difference between the well-established MOSFET device (metal-oxide-semiconductor field-effect transistor) and the SET lies on the device channel concept. Instead of having a conduction channel as in case of MOSFET, which is not allowing further reduction in its length; this channel is replaced by a small conducting "island" or quantum dot (QD).[2] By taking advantage of the Coulomb blockade phenomenon in controlling the transfer of individual electrons to the QD. Source and drain regions are separated from the QD by tunnel junctions. The research on SET is mainly supported on "orthodox theory" based on three assumptions:

- The electron energy quantization inside the conductors is ignored, i.e. the electron energy spectrum is treated as continuous, what is valid only if , where kB is Boltzmann's constant and T is the temperature.

- The time (τt) of electron tunnelling through the barrier is assumed to be negligibly small in comparison with the other time scales. This assumption is valid for tunnel barriers used in single-electron devices of practical interest, where τt ~10-15s.

- Coherent quantum processes consisting of several simultaneous tunnelling events, i.e. co-tunnelling, are ignored. This assumption is valid if the resistance of all the tunnel barriers of the system is much higher than the quantum resistance (~26 kΩ), to confine the electrons to the island.

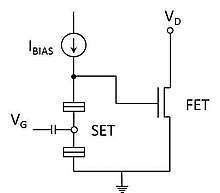

The main benefits of the SET use are a high device integration level and ultra-low power consumption. Moreover, the SET fabrication process is CMOS-compatible (complementary metal–oxide–semiconductor), which increases the possibilities for integrating them into complex circuits. At this point some drawbacks appear to be overcome such as low current level and the low temperature operation. The current level of the SET can be amplified by manufacturing together with a field-effect transistor (FET), by generating a hybrid SET-FET circuit[3][4] (Fig. 2).

Afterwards, the thermal fluctuations can suppress the Coulomb blockade; then, the electrostatic charging energy (e2/C∑) must be greater than kBT. This condition implies the maximum allowed island capacitance is inversely proportional to temperature. For these systems, to solve the drawback related to the SET operative only at cryogenic temperature it should be considered that an island capacitance below 1 aF is required to be room temperature operative. Note that the island capacitance is a function of their size. In this sense, to manufacture room temperature operative SETs the island size should be reduced towards 10 nm. Note that this level of device dimensions can jeopardize the SET manufacturability.

New manufacturing proposals

In this context, the relevance of the SET-based circuits have been recently highlighted through the granting of a project by the European Union, IONS4SET (#688072). The project looks for the manufacturing feasibility of SET-FET circuits operative at room temperature. The main goal of this project is to design SET manufacturability process-flow for large-scale operations seeking to extend the use of the hybrid SET-CMOS architectures. To assure room temperature operation, single dots of diameters below 5 nm have to be fabricated and located between source and drain with tunnel distances of a few nanometers.[5] Up to now there is no reliable process-flow to manufacture a hybrid SET-FET circuit operative at room temperature. In this context, this EU project explores a more feasible way to manufacture the SET-FET circuit by using pillar dimensions of approximately 10 nm.

References

- ↑ S. Mahapatra, V. Vaish, C. Wasshuber, K. Banerjee, and A. M. Ionescu, "Analytical Modeling of Single Electron Transistor for Hybrid CMOS-SET Analog IC Design," IEEE Trans. Electron Devices, vol. 51, no. 11, pp. 1772–1782, Nov. 2004.

- ↑ K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. I. Takagi, and A. Toriumi, "Analytical single-electron transistor (SET) model for design and analysis of realistic SET circuits," Jpn. J. Appl. Phys., vol. 39, no. 4 B, pp. 2321–2324, 2000.

- ↑ A. M. Ionescu, S. Mahapatra, and V. Pott, "Hybrid SETMOS Architecture With Coulomb Blockade Oscillations and High Current Drive," IEEE Electron Device Lett., vol. 25, no. 6, pp. 411–413, Jun. 2004.

- ↑ E. Amat, J. Bausells, and F. Perez-Murano, "Exploring the Influence of Variability on Single-Electron Transistors Into SET-Based Circuits," IEEE Trans. Electron Devices, vol. 64, no. 12, pp. 5172–5180, Dec. 2017.

- ↑ F. Klupfel, A. Burenkov, J. Lorenz, "Simulation of silicon-dot-based single-electron memory devices," Int. Conf. SISPAD, pp. 237–240, 2016.