Motorola 68HC12

The 68HC12 (6812 or HC12 for short) is a microcontroller family from Freescale Semiconductor. Originally introduced in the mid-1990s, the architecture is an enhancement of the Freescale 68HC11. Programs written for the HC11 are usually compatible with the HC12, which has a few extra instructions. The first 68HC12 derivatives had a maximum bus speed of 8 MHz and flash memory sizes up to 128 KB.

| Designer | Freescale Semiconductor |

|---|---|

| Bits | 8-bit/16-bit |

| Design | CISC |

| Encoding | Variable |

| Endianness | Big |

| Registers | |

| 8 | |

Architecture of the 68HC12

Like the 68HC11, the 68HC12 has two 8-bit accumulators A and B (referred to as a single 16-bit accumulator, D, when A & B are cascaded so as to allow for operations involving 16 bits), two 16-bit registers X and Y, a 16-bit program counter, a 16-bit stack pointer and an 8-bit Condition Code Register. Unlike the 68HC11 the processor has 16bit internal data paths

The 68HC12 adds to and replaces a small number of 68HC11 instructions with new forms that are closer to the 6809 processor. More significantly it changes the instruction encodings to be far more dense and adds many 6809 like indexing features, some with even more flexibility. The net result is that code sizes are typically 30% smaller.[1]

HCS12/MC9S12 derivatives

Beginning in 2000 the family was extended with the introduction of the MC9S12 derivatives which have bus speeds of up to 25 MHz and flash sizes up to 512 KB.

The MC9S12NE64 was introduced by Freescale in September 2004, claiming to be the "industry's first single-chip fast-Ethernet Flash microcontroller." It features a 25 MHz HCS12 CPU, 64 KB of FLASH EEPROM, 8 KB of RAM, and an Ethernet 10/100 Mbit/s controller.

MC9S12X derivatives

The MC9S12XDP512 which was introduced in 2004 has a bus speed of 40 MHz and a peripheral co-processor known as the XGATE which allows for some tasks to be offloaded from the CPU. The CPU of the S12X derivative also features several new instructions to increase performance.

Freescale announced the MC9S12XEP100 in May 2006 to further extend the S12X family to 50 MHz bus speed and add a Memory protection unit (based on segmentation) and a hardware scheme to provide emulated EEPROM.

HCS12 products contain a single processor, the HCS12X feature the additional XGATE peripheral processor.

The S12X family offer two main methods to address more than 64KBytes.

- Paged memory regions in the 64 KB local map: PPAGE for paged program data, RPAGE for paged RAM, EPAGE for paged EEPROM/flash

- Global addressing permits access to any addresses in the 8 MB address space. GPAGE is used in conjunction with special opcodes. (gldaa etc.)

XGATE

The XGATE co-processor is a 16-bit RISC processor operating at twice the main bus clock. It offloads work from the S12X core by handling interrupts only and does not run a background loop. The first versions of the XGATE do not allow for higher priority interrupts to pre-empt a currently handled interrupt, but the "XGATEV3" as featured in the 9S12XEP100 (and others) does allow this. The S12X can trigger software interrupts on the XGATE core and vice versa. A semaphore system is implemented to allow the S12X and XGATE cores to synchronize access to peripherals.

Typically the XGATE code is copied to RAM at device startup and then executed from RAM for a speed benefit. The XGATE has a partial 64KByte address space with no paging. The registers share addresses, but the flash and RAM appear at different addresses between the cores. (See the datasheet for more details.)

References

- Sibigtroth, James M. (1996) "Transporting M68HC11 Code to M68HC12 Devices", Motorola Semiconductor Application Note AN1284/D, Motorola.

External links

- Free real-time kernel source code for HCS12 with sample apps

- Freescale's official OpenTCP project on SourceForge for MC9S12NE family

- DRAGON12-Plus HCS12/9S12 Trainer, EVB and Development Board

- MiniIDE development environment that works with both 68HC11 and 68HC12

- 68HC12 Discussion Group

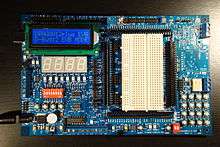

- 68HC12 Development and training system